В рубрику "Решения операторского класса" | К списку рубрик | К списку авторов | К списку публикаций

Интерфейсы и подуровни PHY и MAC

Уникальная особенность уровня 40/100GE PHY (по сравнению с 10GE PHY) состоит в использовании многопотоковой масштабируемой схемы, позволяющей достичь высоких скоростей передачи. Она снижает скорость каждого потока до 10/25 Гбит/с. При этом для уровня PHY не используется подуровень WA N PHY, введенный в 10GE для совместимости c технологией SDH, так как в итоговом стандарте [8] WAN-интерфейсы реализуются на основе рекоммендации G.709 (OTN), а не G.707 (SDH).

Этот стандарт [8] включает все изменения, внесенные в IEEE 802.3-2008, а также новые разделы и приложения. Эти материалы формируют Дополнение (Amendment) 4, содержащее новые параметры подуровня MAC и уровня PHY, а также параметры управления для передачи кадров на скоростях 40/100 Гбит/с.

Во-первых, новая версия добавляет для совместимости 6 новых интерфейсов:

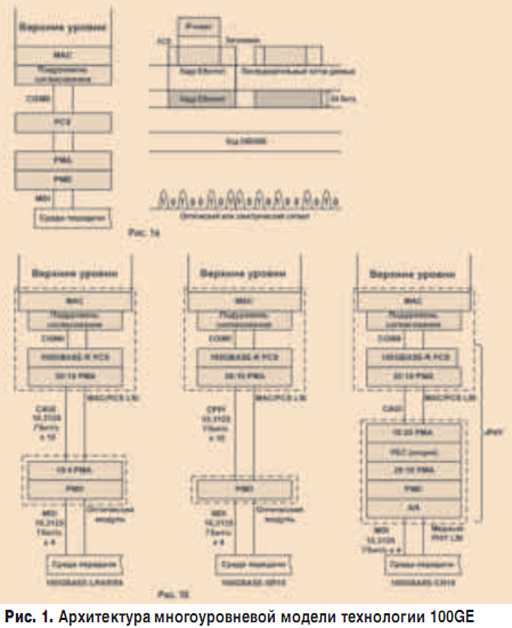

MAC-подуровень и его роль с ростом скорости потока не изменились [9]. Он, как и раньше, преобразует пакеты верхнего уровня в кадры Ethernet, а именно: сегментирует пакеты для инкапсуляции в кадр Ethernet, добавляет к заголовку преамбулу и MAC-адрес, а также формирует контрольную последовательность (FCS) (см. рис. 1 а).

Подуровень согласования (RS) формирует интерфейс между RS и подуровнем кодирования PCS, как логический 100-гигабитный интерфейс CGMII, то есть преобразует (с помощью PCS) последовательные потоки MAC-подуровня в параллельные 64-битные потоки данных (с интерфейсным кодом 64B/66B) (см. рис. 1 а).

CGMII используется как интерфейс между 100GE MAC и уровнем PHY. Ниже он разбивается на 3–5 подуровней: PCS, PMA, PMD, FEC и AN (последних двух нет в 10GE) с интерфейсами между ними: CAUI, CPPI (их нет в 10GE) и MDI (рис. 1 а, б).

Помехоустойчивое кодирование FEC (опционально). Его необходимость определяется подуровнем AN. Он применяется для улучшения уровня BER (версии 100GBASE-CR10 и 40GBASE-CR4/KR4).

Интерфейс CAUI передает поток 100 Гбит/с через десять 10-гигабитных последовательных интерфейсов при оптической передаче на короткие дистанции (100GBASE-CR10) или через четыре 25-гигабитных последовательных интерфейса при передаче на длинные дистанции (100GBASE-LR4). Интерфейс CPPI используется, как и CAUI, для 10-потоковой передачи общего 100-гигабитного потока на короткие дистанции (100GBASE-SR10).

В логических блоках MAC/PCS LSI (рис. 1 б) на подуровне PCS 66-битные блоки данных с кодом 64B/66B распределяются циклически по 20 логическим потокам. Учитывая, что после 64B/66B-кодирования скорость 100G-сигнала становится 103,125 Гбит/с, получаем, что скорость одного логического потока – 5,15625 Гбит/с. В подуровне PMA указанные 20 потоков можно конвертировать (путем мультиплексирования с бит-интерливингом [3]) в требуемое число физических потоков (кратность выхода 1, 2, 4, 5 и 10). Стандарт поддерживает только кратности 4 и 10. В первом случае скорость физического потока составит 25,78125 (100/4), а во втором – 10,3125 Гбит/с (100/10).

Так как число исходных логических потоков велико (20), могут возникнуть перекосы из-за джиттера и различия времени прихода. Они компенсируются вставкой (через каждые 16 383 кодовых 66-битовых блока) специальных выравнивающих 66-битовых маркеров, содержащих номер логического потока и поле проверки на четность чередующихся бит типа BIP.

Подуровень PMA осуществляет конвертирование 20:10 для формирования 10-гигабитных потоков и 10:4 для формирования 25-гигабитных потоков.

Подуровень FEC включается для формирования вариантов 40/100GBASE-R FEC, используемых при передаче по медной паре (или при применении на задней панели компьютеров) и позволяющих на 2 дБ улучшить BER и исправлять пачки ошибок. Для этой цели применяется укороченный циклический код Файера (Fire code – FC) с 32-битной четностью (для каждого потока), позволяющий исправлять пачки ошибок длиной до 11 бит [9, 10].

В результате для 40/100GE получаем следующую картину подуровней физического уровня.

Интерфейс MII (Media Independent Interface), независимый от среды передачи, – обеспечивает логическое соединение между MAC-подуровнем и составляющими уровня PHY. Он не требует физической реализации и соединяет уровни внутри какого-то устройства логически.

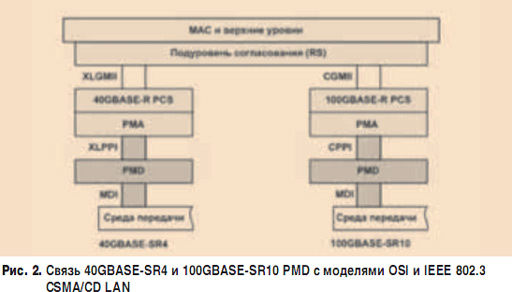

Интерфейс XLGMII – поддерживает 40-гигабитные, а интерфейс CGMII – 100-гигабитные операции в процессе передачи/приема проходящих через них 64-битных потоков данных, тогда как подуровень RS обеспечивает отображение между сигналами, формируемыми интерфейсами XLGMII и CGMII и спецификациями сервиса MAC/PLS. Несмотря на то что интерфейсы XLGMII и CGMII опциональны, они широко применяются в стандарте как основа для функциональной спецификации, и обеспечивают общий сервисный интерфейс для подуровней физического кодирования, определенных в стандарте [8].

Термины 40/100GBASE-R относятся к особой группе реализаций интерфейсов физического уровня, основанной на методе блочного кодирования данных кодом 64B/66B и спецификации PMA. 40/100GBASE-R PCS осуществляют: кодирование/декодирование данных, полученных от интерфейсов (или переданных на интерфейсы) XLGMII/CGMII в виде блоков кода 64B/66B; распределение данных по нескольким параллельным потокам (lanes) и передачу данных на PMA.

Подуровень FEC – опционален для 40/100GBASE-R, рассчитанных на передачу по медной паре (STP) или передачу на задней панели PHY. Он может быть помещен между подуровнями PCS и PMA или между двумя подуровнями PMA, реализуется для каждого потока PCS (PCS-lane) отдельно и работает автономно для каждого потока PCS.

AN – подуровень согласования необходимости использовать кодирование FEC, обеспечивающий наличие такого подключенного устройства, которое может обнаружить на другом конце звена связи устройство, обладающее таким же режимом работы, и, определив наличие общих возможностей, сконфигурировать реализацию совместной операции. AN используется 40-гигабитной задней панелью уровня PHY для поддержки Ethernet типа 40GBASE-KR4 и потоков 40/100 Гбит/с по STP физического уровня для поддержки Ethernet типа 40GBASE-CR4 и 100GBASE-CR10.

Подуровень PMA обеспечивает для PCS независимое от среды передачи средство поддержки использования различных физических сред передачи. Дополнительно он осуществляет (по требованию) ретайминг (восстановление синхронизации) принятых данных и обеспечивает их тестирование и общий контроль.

Подуровень PMD отвечает за интерфейс данных, передаваемых в среду передачи, и располагается непосредственно над интерфейсом MDI, который относится к категории элементов, включаемых в каждый подуровень PMD, и фактически является подсоединением к среде передачи.

Цель интерфейсов XLAUI/CAUI – обеспечить гибкое соединение между двумя ИС или между ИС и модулем для 40/100-гигабитных компонентов при длине соединения на печатной плате до 25 см, включая разъем. Интерфейс CAUI может обеспечить соединение между 10-поточным подуровнем PMA (скорость передачи 100 Гбит/с) и элементом отображения 10:4 PMA. А интерфейс XLAUI может обеспечить удлинение потока для соединения распределенных на печатной плате компонентов MAC и PHY уровней в системе 40-гигабитного Ethernet.

Интерфейс XLAUI/CAUI имеет следующие характеристики:

Параллельный физический интерфейс (nPPI) – это реализация сервисного интерфейса PMD. Он позволяет конструировать компактные модули оптических трансиверов для 40GBASE-SR4/LR4 или 100GBASE-SR10. 40-гигабитный PPI (XLPPI, 4 потока) используется с 40GBASE-SR4/LR4, а 100-гигабитный PPI (CPPI, 10 потоков) – с 100GBASE-SR10.

Подуровни PMD и PMA нужно подключать к интерфейсам nPPI, чтобы удовлетворить требования по задержке, перекосу и вариации перекоса.

Опциональный интерфейс MDIO/MDC – интерфейс ввода-вывода данных менеджмента (или интерфейс управления) обеспечивает соединение между управляемыми устройствами MDIO (MMD) и логическими объектами управления рабочими станциями (STA).

Из 8 вариантов (типов интерфейсов) Ethernet (см. табл. 2) мы рассмотрим особенности реализации пяти вариантов, собранных в две группы: 40/100GBASE-SR4/10 и 40/100GBASE-LR4+ER4. Первая группа позволяет передать 4/10 потоков на расстояние 100 м по ММ ВОК в первом окне прозрачности, тогда как вторая – позволяет передать 4 потока на расстояние 10/40 км по ОМ ВОК во втором окне прозрачности.

Реализуемые варианты (см. модели физического уровня на рис. 2) передают потоки по двум схемам:

RS? XLGMII? 40GBASE-R PCS?PMA?XLPPI?PMD?MDI?Me dium;

RS? CGMII? 100GBASE-R PCS? PMA? CPPI? PMD?MDI? Medium.

Определяющими здесь являются: подуровень PMD с интерфейсами XLPPI/CPPI и MDI (выделены на рис. 2), хотя для формирования полного PHY-уровня PMD должен быть соединен с соответствующим PMA, как показано на рис. 2, со средой (через интерфейс MDI). При этом 40GBASE-SR4 использует 4, а 100GBASE-SR10 – 10 идентичных потоков (lanes), пронумерованных от 0 до n-1, n=4 или 10.

Сервисные интерфейсы для 40GBASE-SR4 и 100GBASE-SR10 PMD описаны достаточно абстрактно и не подразумевают какое-то конкретное исполнение, хотя логически поддерживают обмен кодированными данными между объектами PMA и PMD, транслируя данные в сигналы, подаваемые в среду или принимаемые из нее. Суммарная задержка сигнала при прохождении PMD (с учетом 2 м ВОК) не должна превышать для 40GBASE-SR4 1024 БТ, а для 100GBASE-SR10 – 2048 БТ.

Для Ethernet типа 40/100GBASE-LR4 и 100GBASE-ER4 блок-схема приведена на рис. 3. Интерфейс PMD здесь выполняет функции приема-передачи, которые доставляют данные между сервисным интерфейсом PMD и интерфейсом MDI.

Функция передачи PMD конвертирует 4 электрических в 4 оптических потока, доставляемых на интерфейс MDI. Функция приема PMD конвертирует 4 оптических потока, полученных от MDI, в 4 электрических потока для доставки на сервисный интерфейс PMD. Причем параллельные потоки собираются/разбираются на стороне передачи/приема с помощью мультиплексоров/демультиплексоров WDM и используют ОМ ОВ ВОК в качестве среды передачи для достижения большей длины передающего тракта (см. табл. 2).

Подуровень PMD стандартизован в тестовых точках (TPn). Электрический сигнал на передающей стороне (PMA-PMD) определяется в точке TP1; оптический – в точке TP2 (на выходе 2–5 м ОВ-патч-корда); оптический сигнал приема – в точке TP3 (на выходе ММ ВОК у интерфейса MDI); электрический сигнал на приемной стороне (PMD-PMA) определяется в точке TP4.

Аналогично предыдущей будет выглядеть и блок-схема для двух других типов Ethernet: 40GBASE-SR4 и 100GBASE-SR10. Ее отличие в том, что число конвертируемых потоков будет различно: 4 для Ethernet 40GBASE-SR4 и 10 для Ethernet 100GBASE-SR10, а параллельные потоки не будут собираться/разбираться на стороне передачи/приема с помощью мультиплексоров/демульти-плексоров WDM, а будут передаваться отдельно.

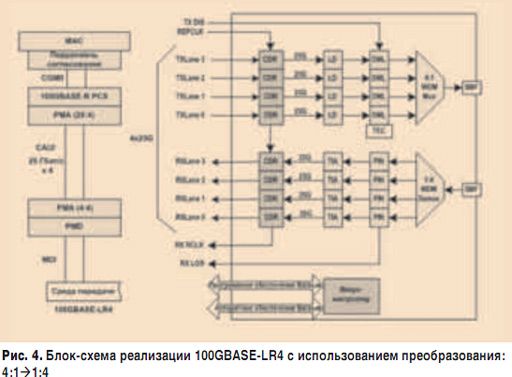

Рассмотрим более подробно возможные схемы реализации 100GBE типа 100GBASE-LR4.

Согласно стандарту [8] и рис. 3 этот тип Ethernet реализуется по 4-поточ-ной схеме с WDM-мультиплексированием 4 несущих: 1295, 1300, 1305 и 1310 нм, выбранных во втором окне прозрачности по стандартной сетке ITU-T G.694.1 с шагом 800 ГГц [7]. Передача в дуплексном режиме осуществляется по двум ОВ.

Если для реализаций 100GbE, ориентированных на использование электрических сигналов, характерно применение 10-гигабитных потоков, то для реализаций, ориентированных на оптические сигналы, характерно применение 25-гигабитных потоков. На эту схему ориентирована в целом и реализация 100GBASE-LR4. Здесь логично использовать и 25-гигабитные электрические потоки (как предложил Форум оптического сетевого взаимодействия – OIF).

Однако для модулей первого поколения была использована архитектура с электрическим интерфейсом 10-гигабитного 10-поточного CAUI (10х10 Гбит/с), учитывая наличие готовых модулей, разработанных для 10GE. Она требовала использования сериа-лайзера на передающей стороне модуля, конвертирующего 10 потоков в 4 (10:4), и десериалайзера на приемной стороне модуля, осуществляющего обратную конвертацию (4:10). Но эти конвертеры увеличивали энергопотребление модуля, ширину интерфейса CAUI и размеры модуля.

Этого можно избежать, используя 25-гигабитный электрический интерфейс, предлагаемый OIF. На этом и основана блок-схема реализации 100GBASE-LR4 нового поколения с более простой схемой преобразования: 4:1?1:4, приведенной на рис. 4. При отсутствии блоков конвертации энергопотребление модуля существенно ниже, а его размеры практически сводятся к размерам модуля 10GBE [11].

Литература

Статья поступила в радакцию журнала ТСС 31.05.2011 г.

Опубликовано: Журнал "Технологии и средства связи" #1, 2012

Посещений: 18609

Статьи по теме

Автор

| |||

В рубрику "Решения операторского класса" | К списку рубрик | К списку авторов | К списку публикаций